Brain-inspired, or neuromorphic computing, has attracted tremendous interest from both academia and industry in the past decade due to its higher energy-efficiency as compared to conventional computing based on the von-Neumann architecture. Among the many reasons why the brain is so energy-efficient and fault-tolerant in cognitive tasks are its high connectivity (1014 synapses) and distributed architecture. In order to reproduce, or at least approach the capability of a brain, two components are necessary:

High-k metal gate charge trapping transistors (CTTs) are utilized in this research as analog synapses. CTTs are standard CMOS transistors that leverage the stabilized charge-trapping behavior in the high-k gate dielectric. This technological approach requires only the use of mature CMOS processes, thus reducing the manufacturing complexity. A system-on-wafer integration approach based on silicon interconnect fabric (Si-IF) is used for this research. In this methodology, chips can be integrated directly on a Si wafer substrate in high proximity (edge to edge distance of approximately 50 µm). Each die is connected using a small-pitch (~10 µm) vertical interconnect array. Using CTTs as analog synapses within a Si-IF based integration methodology will enable the design of a large-scale neuromorphic system that will be energy-efficient and fault-tolerant in cognitive tasks, mimicking the human brain.

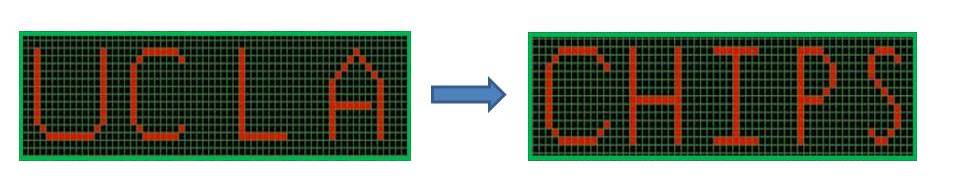

Reprogrammability of a CTT array from "UCLA" to "CHIPS"

[Source: F. Khan et al., EDL, 2017.]